# ZEROLAB A-O "Divided by O PEDAL" 設計報告書

2025年 10月 1日

**ZEROLAB**

## 目次

## **仕様---** p. 2

- **1. 電源部---** p. 3∼7

- 1.1 プリアンプ電源昇圧部--- p.3~6

- 1.2 ヒーター電源降圧部--- p.7

- **2**. ファンコントローラ--- p. 8~9

- 3. プリアンプ--- p. 9

- 4. JC-120 補正回路/キャビネットシミュレータ--- p. 10~13

### 最終決定仕様

| 電源電圧      | 18 V                 |

|-----------|----------------------|

| 定常消費電流    | 400 mA               |

| 瞬間消費電流    | 1000 mA              |

| 入力インピーダンス | $56\mathrm{k}\Omega$ |

| 出力インピーダンス | $470\Omega$          |

設計上の電流最大値は1000[mA]であるが、Vital Audio VA-08Mk-Ⅱ/18[V]800[mA]で起動確認済み。

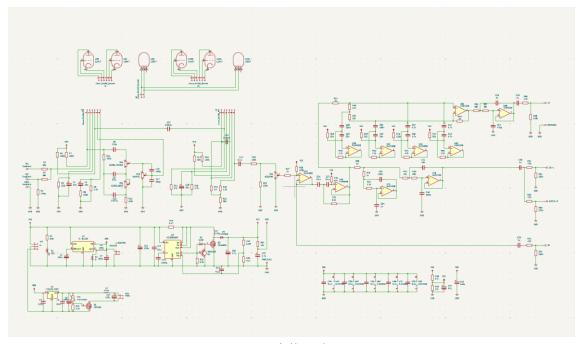

図2 全体回路図

## 1. 電源部の設計

## 1.1 プリアンプ電源昇圧部

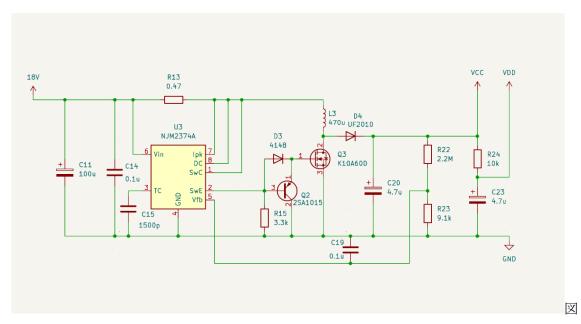

2 昇圧 DCDC コンバータ回路図

項目

記号

Unit

入力電圧

V<sub>IN</sub>

18

V

出力電圧

V<sub>OUT</sub>

300

V

出力電流

I<sub>OUT</sub>

2.07

mA

表 2 目標仕様

プリアンプ回路の消費電流はアンプ実機の計測から、 $V_{cc}=300$  [V]において 2.07 [mA]であった。

この電源を供給する DCDC コンバータを設計する。

リプル周波数が可聴域外になるようにするため、スイッチング周波数が任意に設定できる PWM 型の DCDC コンバータ IC を使用する。入手性から NJM2374A を採用した。

表3選定インダクタ仕様・定格

SUMIDA SMD Power Inductor CDRH127/LDNP-471MC

| 項目      | 記号    |                  | Unit    |

|---------|-------|------------------|---------|

| 定格電流    | $I_L$ | 1.00             | A       |

| インダクタンス | Н     | $470\!\pm\!20\%$ | $\mu$ H |

| DC 抵抗 | $R_{DC}$ | 741 | mΩ |

|-------|----------|-----|----|

|       |          |     |    |

$\underline{https://products.sumida.com/products/pdf/CDRH127LD\%20(en).pdf?t=1755201134}$

入力電圧 18[V]出力電圧 300[V]と昇圧比が高いため、高インダクタンスのインダクタが必要である。ここでは入手性を考慮し、470[uH]のインダクタを使用する。

表 4 選定 MOSFET 定格

TOSHIBA Nch パワーMOSFET TK10A60D S5Q

| 項目          | 記号        |     | Unit |

|-------------|-----------|-----|------|

| ドレイン・ソース間耐圧 | $V_{DSS}$ | 600 | V    |

| ゲート・ソース間耐圧  | $V_{GSS}$ | ±30 | V    |

| ドレイン電流      | $I_D$     | 10  | A    |

https://toshiba.semicon-storage.com/info/datasheet\_ja\_20180619.pdf?did=5939

表5選定ダイオード仕様・定格

PANJIT INTERNATIONAL INC. UF2010

| 項目    | 記号        |      | Unit |

|-------|-----------|------|------|

| 耐圧    | $V_{DSS}$ | 1000 | V    |

| 順方向電圧 | $V_F$     | 1.7  | V    |

| 許容順電流 | $I_{AV}$  | 2.0  | A    |

https://www.panjit.com.tw/upload/datasheet/UF200G\_SERIES.pdf

いずれにおいても目標電圧300 [V]よりも十分高い耐圧を確保できている。

#### 電力、許容電流の検証

デューティ比Dを求める。

入出力1周期当たりエネルギー等式

$$\eta \frac{1}{2} H I_P^2 = \frac{V_{OUT} I_{OUT}}{f_{SW}} \tag{1}$$

電圧、電流、インダクタンスの関係式

$$V = H \frac{dI}{dt} \tag{2}$$

$$V_{IN} = H \frac{I_P}{t_{on}} \tag{3}$$

(1)、(3)より、

$$\eta \frac{V_{IN}^2 t_{on}^2}{2H} = \frac{V_{OUT} I_{OUT}}{f_{SW}} \tag{4}$$

$t_{on}$ について解いて、

$$t_{on} = \sqrt{\frac{2V_{OUT}I_{OUT}H}{\eta f_{SW}V_{IN}^{2}}} \tag{5}$$

デューティ比Dについて、

$$D = t_{on} f_{SW} \tag{6}$$

なので、(5)、(6)より、デューティ比Dが求められる。

$$D = \sqrt{\frac{2V_{OUT}I_{OUT}Hf_{SW}}{\eta V_{IN}^2}} \tag{7}$$

スイッチング周波数 $f_{SW}$ は可聴域外 20[kHz]<  $f_{SW}$ を満たすようにする。

DCDC コンバータ IC NJM2374A データシート p5発振周波数対タイミングキャパシタ特性例より、

タイミングキャパシタ $C_T = 1000[pF]$ で $f_{SW} \approx 31[kHz]$ となる。

https://www.nisshinbo-microdevices.co.jp/ja/pdf/datasheet/NJM2374A\_J.pdf

回路に流れる電流最大値Ipを求める。

(1)を $I_p$ について解いて、

$$I_P = \sqrt{\frac{2V_{OUT}I_{OUT}}{\eta H f_{SW}}} \tag{8}$$

$f_{SW}=31[{

m kHz}]$ においての効率 60[%]を仮定して $I_P$ を求めると、 $I_P=377[mA]$ となる。 これはインダクタの定格電流 $I_L=1.00[A]$ の半分以下であり、電流によるインダクタンス の低下は許容範囲内である。また、スイッチの定格にも電流、許容損失ともに十分余裕が ある。

#### 効率の測定

計測より、 $C_T=1500[{

m pF}]$ 、 $f_{SW}=41[{

m kHz}]$  ( $T_a=25\,[{

m ^{\circ}C}]$ )で DCDC コンバータ全体の平均消費電流 $I_{IN}$ が最小値

$$I_{IN} = 46.6 [mA]$$

となった。 $V_{IN}, I_{IN}, V_{OUT}, I_{OUT}$ より、入力電力 $P_{IN}$ 出力電力 $P_{OUT}$ が

$$P_{IN} = V_{IN}I_{IN} = 18 \times 46.6 \times 10^{-3} \approx 0.839 \, [W]$$

$$P_{OUT} = V_{OUT}I_{OUT} = 300 \times 2.07 \times 10^{-3} = 0.621 [W]$$

となった。これらより、効率 $\eta$ ,損失 $P_{LOSS}$ は

$$\eta = \frac{P_{OUT}}{P_{IN}} \approx 74[\%]$$

$$P_{LOSS} = P_{IN} - P_{OUT} \approx 0.22$$

[W]

と求まった。各部品の許容損失よりも十分に小さい。

#### 過電流保護抵抗 R12 について

DCDC コンバータ IC NJM2374A の 7pin は電流監視

6pin-7pin の電位差が 300[mV]以上になると PWM パルス出力が停止する。

インダクタとパワーサプライの電流供給能を考慮し、制限抵抗を  $0.47[\Omega]$ としたとき、制限電流 $I_{lim}$

$$I_{lim} = \frac{300 \times 10^{-3}}{0.47} = 638 \ [mA]$$

となるようにした。

#### 分圧抵抗 R23, R24 について

NJM2374Aの 5pin スレッシホールド電圧 $V_{th}$ は 1.250±2%[V]となっている。

出力電圧は以下の式で決定される。

$$V_{OUT} = 1.250(1 + \frac{R23}{R24})[V]$$

E24 系列から、R23 =  $2.2[M\Omega]$ 、R24 =  $9.1[k\Omega]$ のとき、

$$V_{OUT} = 1.250 \left( 1 + \frac{2.2 \times 10^6}{9.1 \times 10^3} \right) \approx 303 [V]$$

と、目標電圧に近い電圧が得られた。

また、抵抗誤差±1[%]の抵抗を使用する。

#### 1.2 ヒーター電源降圧部

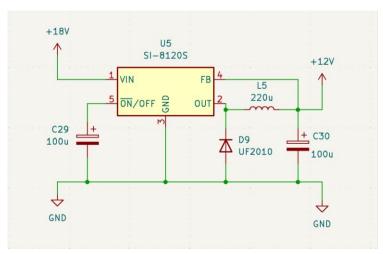

図3 降圧 DCDC コンバータ回路図

12AX7のヒーター電圧/電流は12.6V/150mAである。

2 本並列で動作させるので 12V/300mA の電源を用意する。

また、昇圧部と電源投入時の電流ピークをずらし、ヒーター突入電流を制限するために、スロースタートを利用する。

| 項目   | 記号               |     | Unit |

|------|------------------|-----|------|

| 入力電圧 | $V_{in}$         | 18  | V    |

| 出力電圧 | $V_{out}$        | 12  | V    |

| 出力電流 | I <sub>out</sub> | 300 | mA   |

表 6 目標仕様

スイッチ内蔵型の DCDC コンバータ IC を利用する。

12V 固定出力、外付け部品数4の SI-8120S を採用した。

発振周波数 60kHz と可聴域外でスイッチングし、18V 電源ラインに乗るリプルはある程度 無視できる。

https://www.semicon.sanken-ele.co.jp/sk\_content/si-8120s\_ds\_jp.pdf

#### 2. ファンコントローラ

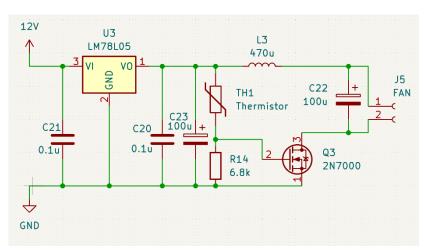

図4 ファンコントローラ回路図

DCDC コンバータ、真空管から熱が発生する、真空管アンプではケース外に真空管を配置するため熱は問題にならないが、小型のケース内に配置しケース内部が高温になる。これは電解コンデンサの寿命に大きく影響する。そこで放熱に 12VDC ファンを使用する。このファン出力 100%で使用すると、電源に混入するノイズが無視できないものになり、放熱性能もオーバースペックとなる。そこでリニアレギュレータで降圧する。リニアレギュレータの発熱を減らすため、電源はヒーター用電源 12V を使用する。

さらに、低温時に無回転となるように、サーミスタで温度変化を反映する。 サーミスタと R14 で分圧し、目的の温度で MOSFET のゲートスレッショルド電圧 2.1[V]になるようにする。

表 7 選定 MOSFET 仕様

ON Semiconductor Nch MOSFET 2N7000

| 項目           | 記号       |     | Unit |

|--------------|----------|-----|------|

| ゲートスレッショルド電圧 | $V_{GS}$ | 2.1 | V    |

https://akizukidenshi.com/goodsaffix/2n7000\_20210601.pdf

表8選定サーミスタ仕様

Semitec NTC サーミスター 103AT-2-34119

| 項目   | 記号       |                | Unit |

|------|----------|----------------|------|

| 抵抗 1 | $R_{25}$ | 10k            | Ω    |

| B 定数 | В        | $3435 \pm 1\%$ |      |

https://akizukidenshi.com/goodsaffix/assy.pdf

目的の ON となる温度を T=50[℃]とすると、

$$R = R_0 \times \exp\left\{B\left(\frac{1}{T + 273} - \frac{1}{T_0 + 273}\right)\right\}[V]$$

から T=30[℃]におけるサーミスタの抵抗値

$R=8.27k[\Omega]$ と求まる。

このときにゲート電圧が 2.1[V]となるように、R14の抵抗値を求めると、

$$\frac{R_{14}}{R + R_{14}} = \frac{2.1}{5.0}$$

R14=5.987 k[Ω]と求まり、

E11 系列から 5.6 $k[\Omega]$ と仮決定した。

ゲート電圧 2.1[V]時の DC ファン端子間電圧と回転開始電圧とにはギャップがある。 そこで、ブレッドボード上で R14 の値を複数パターン試したところ、

$R=6.8k[\Omega]$ としたと きに目的の動作が得られた。

#### ノイズ対策

ファン回転によるノイズは可聴域にあり無視できない。 そこでノイズ対策としてn型LCフィルターを設けた。

## 3. プリアンプ

プリアンプ部の回路、各種部品について、筐体内に収まるサイズの部品を選びつつ、下 記資料の定数にできるだけ近いものとする。

https://blogger.googleusercontent.com/img/b/R29vZ2x1/AVvXsEjTVYcA\_r2RwMQ1e8BvH03bArZ6cIbd4iBz9FT4YipBLmzXy7b32GpXRSglbIMKi1f3270h9VY2JKUYBa7J22tV8ci1VbFK74bgGZr00Z3Sc2WJLQpcmH2bjFyJUSL6Zu0LTXpS9Pf9WtE/s1600/CeeJayEleven.jpg

Phase inverter 段について:

実機は後段にプッシュプルパワーアンプがあり、プレート,カソード両方から信号を取り出しているが、本設計ではライン出力とするため、プレート側の出力、カップリングコンデンサは omit する。プリアンプ全体で正相となるカソード側から信号を取り出す。後段のバッファ部も非反転増幅とする。

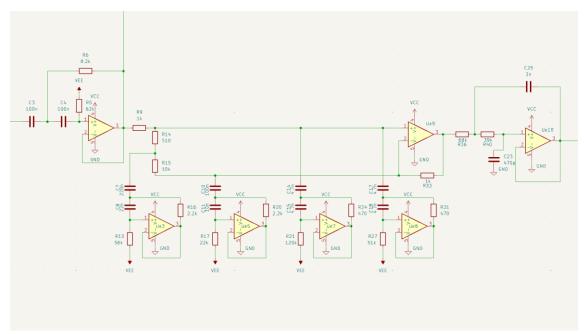

#### 4. JC-120 補正回路/キャビネットシミュレータ

#### 目標仕様

本プリアンプはアンプの RETURN 端子接続を前提として設計している。しかし、アンプによってはマスターボリュームが機能しない機種が存在し、スタジオやステージで多用される Roland JC-120 もその一例である。この場合、プリアンプ側のマスターボリューム操作により JC-120 の定格出力である 120 Wがそのまま発生し、実用上の音量調整が困難となるという問題がある。

この課題に対応するため、本設計では JC-120 本体側のボリュームを有効に活用できるよう、プリアンプをフロント入力端子に接続する方式を併用可能とした。その際、イコライザーを 5 / 5 / 5 に設定した場合にキャビネットの周波数特性が正しく再現されるよう、特性補正回路をプリアンプ内に組み込み、フロント入力接続時においても音質バランスが維持されることを目標とした。

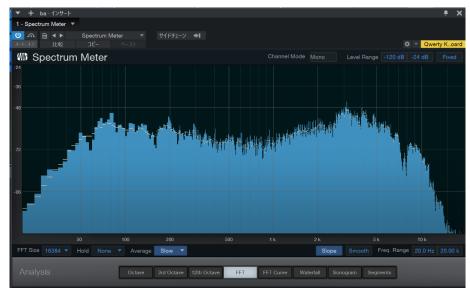

図5 実機周波数特性

図 5 はコピー元アンプ同パーツ、同配置、同キャビネット形状で再現したアンプの周波数解析結果である。この周波数特性を目標とする。

以下に簡単な測定手順と測定環境を示す。

マイク Marantz MPM1000

マイキング位置 センター

オーディオインターフェース Arturia Minifuse2

表 9 測定機材

#### 測定手順

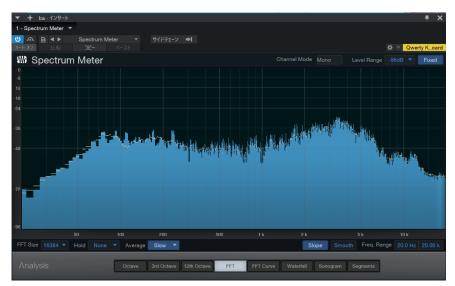

- ・アンプ INPUT にピンクノイズを入力する。

- ・DAW 上で FFT アナライザを起動

- ・十分な時間をおき、Average が安定したタイミングでスクリーンショット

同じ機材を用いて同様の手順でプリアンプペダル+JC120 の周波数解析を行った。 ただし、プリアンプペダルの INPUT にピンクノイズを入力し、OUTPUT を JC120channe12 LOW に入力し、左側スピーカーで測定を行った。

図 6 プリアンプ+JC120 周波数特性

この周波数特性の差を埋めるために、プリアンプ後段にイコライザ回路を設けることを 検討する。

プリアンプ OUTPUT をインターフェースに入力、DAW の EQ で出力を JC120 に入力 して再度測定を行う。回路で実装するフィルタ数が有限であることを考慮し、5band+ハイ /ローカットで調整したところ、以下の設定で近い周波数特性が得られた。

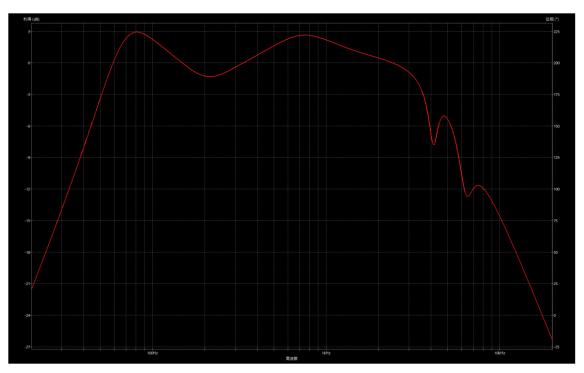

図7 イコライジングカーブ

図8 プリアンプ+JC120 補正後周波数特性

このQ値、ゲイン、周波数はそのままオペアンプを用いたイコライザ回路(半導体インダクタ)の計算に転用できる。ただし、ハイ/ローパスフィルタは 12[dB/Oct]=24[dB/Dec]となることに注意する。

図 9 周波数特性補正回路図

図 7 の 75[Hz]のピーキングはサレンキー型二次フィルタのQ値をQ>1 とすることで再現し、並列疑似インダクタ数を 4 とした。

上記回路の SPICE シミュレーション結果である。図7の曲線が概ね再現されていることが確認できる。

図10 周波数特性補正回路シミュレーション結果

#### 参考資料:

昇圧コンバータの電力段に関する基本的な計算の2022 Texas Instruments <a href="https://www.ti.com/jp/lit/an/jaja713d/jaja713d.pdf?ts=1755237250683&ref\_url=https://swww.ti.com/jp/lit/an/jaja713d/jaja713d.pdf?ts=1755237250683&ref\_url=https/253A%252F%252Fwww.ti.com%252Fsolution%252Fja-jp%252Fe-reader

#### その他部品リンク

可変抵抗 https://www.linkman.jp/data/R1610N-QA1.pdf